0. Sequential System

1) finite state machine

state는 현재 0 또는 1의 값을 의미하므로 memory로 생각해도 된다.

그러므로 유한한 메모리를 저장하는 machine을 말한다.

1> memory를 가진 system

2> output은 [1] 현재 input과 [2] 과거 history를 통해 결정합니다.

2) Synchronous system

clock이 input, internal, output signal에 영향을 미칩니다.

cf> Clock

일정 속도로 0과 1이 반복되는 signal

cf> Latch

1-bit를 저장하는 메모리

1. Latch

1) SR Latch

0> boolean function

1> 회로도

2> Truth table

- (S, R) = (0, 0)인 경우, Q+ = Q

- (S, R) = (1, 0)인 경우, Q = 1

- (S, R) = (0, 1)인 경우, Q = 0

- (S, R) = (1, 1)은 정의되지 않았습니다.

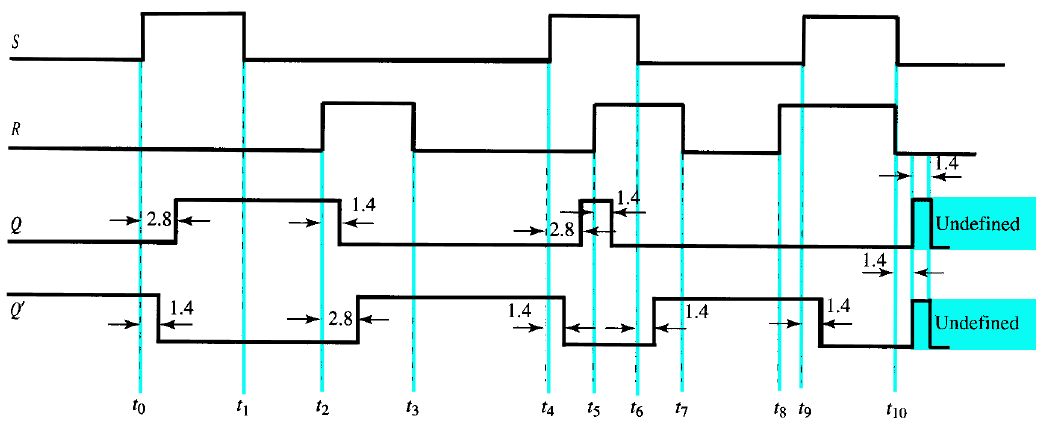

3> SR Latch timing

- Gate Delay 이해하는 방법

아래 식에서 무엇이 바껴서 그 다음에 또 무엇이 바뀌는지 파악

t0에서 [1] S가 변하고 위의 식에 의해 [2] Q'가 변합니다. (1.4) 그리고 위의 식에 의해 [3] Q가 변합니다.(2.8)

- 하지만 (S, R) = (1, 1)인 부분이 존재하는 문제가 있습니다.

이를 극복하기 위해 clock을 이용합니다.

2) Gated Latch

1> 회로도

Gate라는 enable을 추가한 형태입니다.

2> Truth Table

Gate = 0 -> (SG, RG) = (0, 0) -> Q = Q+

Gate = 1 -> SR Latch

3) Clocked SR Latch

1> 회로도

2> Truth Table

C = 0 -> Q+=Q

C = 1 -> SL Latch

4) Gated D Latch

1> 회로도

2> Truth Table

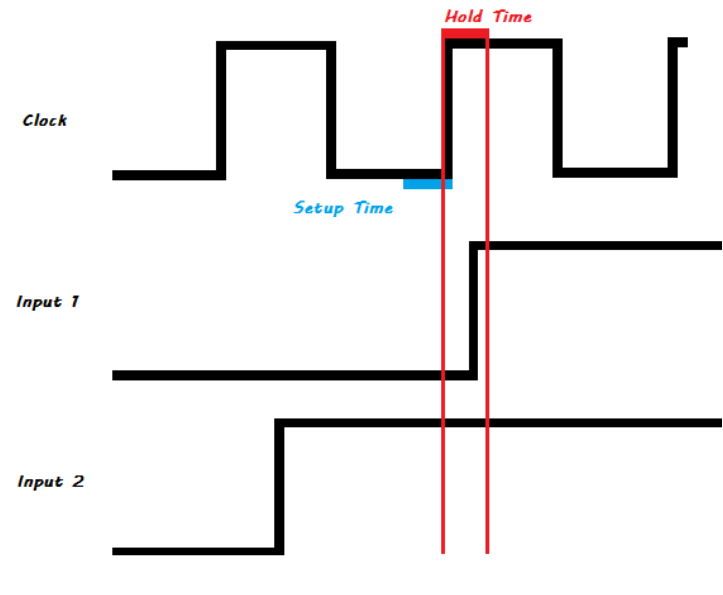

cf> Setup time & Hold time

[1] setup time : rising(falling) edge 전, input을 입력으로 받아들이는데 필요한 최소 시간

- input 1은 0과 1 모두 setup time 동안 특정값을 유지하지 못해서 setup time을 만족하지 못합니다.

- input 2는 setup time동안 0의 값을 일정하게 유지해서 setup time을 만족합니다.

[2] hold time : rising(falling) edge 후, output을 출력으로 유지하는데 필요한 최소 시간

- input 1은 0과 1 모두 hold time 동안 특정값을 유지하지 못해서 hold time을 만족하지 못합니다.

- input 2는 hold time동안 0의 값을 일정하게 유지해서 hold time을 만족합니다.

3> Gated D latch timing

3번째 clock에서 D가 setup time을 만족하지 못하자 Q의 값이 중간에 떨어지는 현상을 볼 수 있다.

'디지털 회로 개론' 카테고리의 다른 글

| 6-1강 - Sequential Circuit Design 1 (Finite State Machine, Moore Machine & Mealy Machine) (0) | 2020.11.16 |

|---|---|

| 5-2강 - Analysis of Sequential Systems 2 (Flip Flops) (0) | 2020.11.13 |

| 4-4강 - Combinational System Design 4 (ROM, PLA, PAL) (0) | 2020.10.23 |

| 4-3강 - Combinational System Design 3 (Multiplexers, Bus) (0) | 2020.10.22 |

| 4-2강 - Combinational System Design 2 (Adder/Subtractor, Decoder) (0) | 2020.10.22 |