8. ROM

한 번 기록한 정보는 반영구적으로 기억되며 (첫 내용 작성에 특수 기기가 필요하고),

삭제나 수정이 불가능한 기억장치를 가리킨다. (동적으로 write할 수 없는 장비이다.)

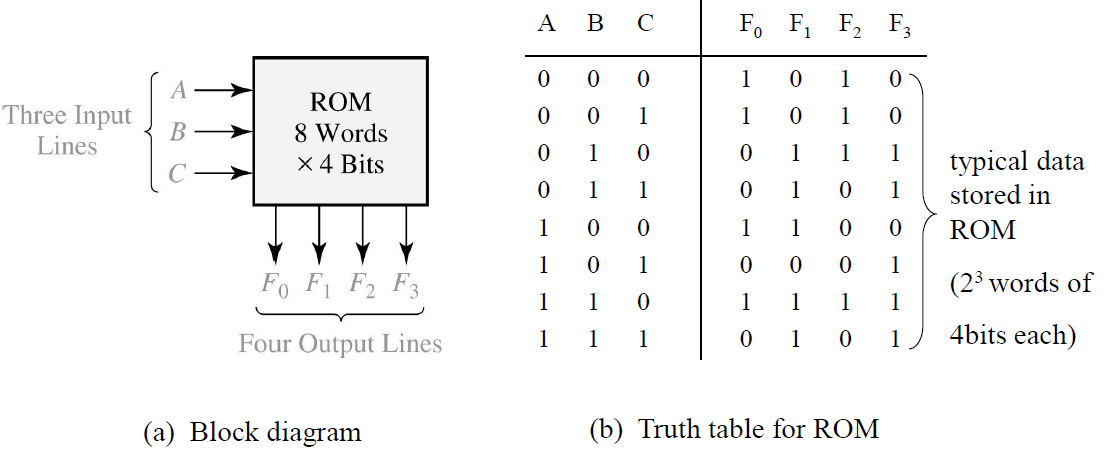

1) 예시 (8-Word X 4-bit ROM)

8이라는 word가 들어가려면 3개의 input lines을 필요로 한다. (2^3 = 8)

4개의 output line을 가진다.

1> Truth Table

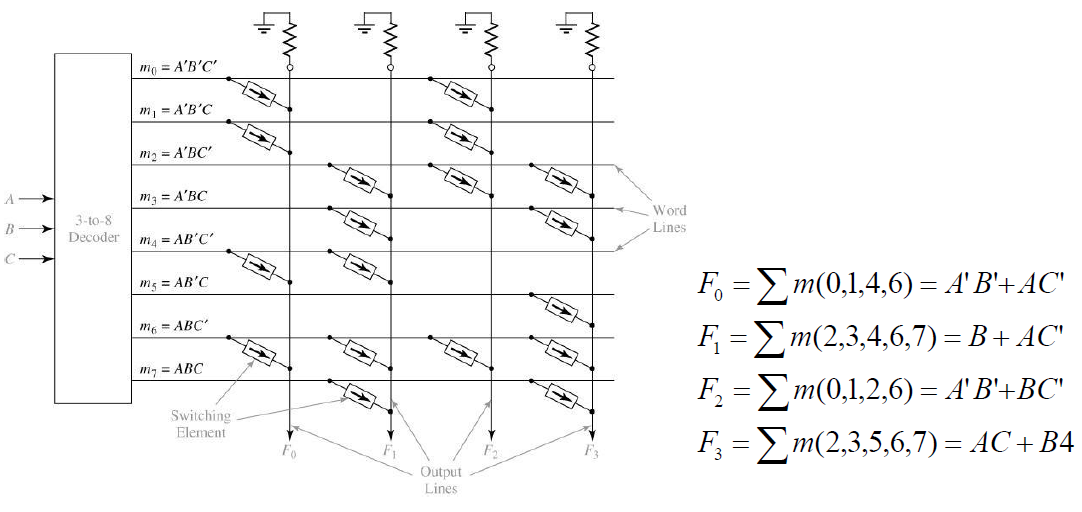

2> 회로

먼저 decoder로 3개 input을 8개의 minterm으로 변환한다.

truth table을 기반으로 각 F_0~F_3을 minterm꼴로 나타낸다.

그리고 minterm을 기반으로 아래와 같이 switching element를 연결한다.

3> 장점 : 미리 만들어두고 빨리 구현할 수 있다.

4> 단점 : 연결이 빈 공간이 많으면 효율적이지 못하다.

2) Read-Only Memory

1> programmable versions of the conceptional AND and OR gate

=> SOP form이다.

2> connection은 칩을 제조하는 과정에 만든다.

3> 실제로는 모두 연결되어 있고 필요 없는 connection을 끊어가며 만든다.

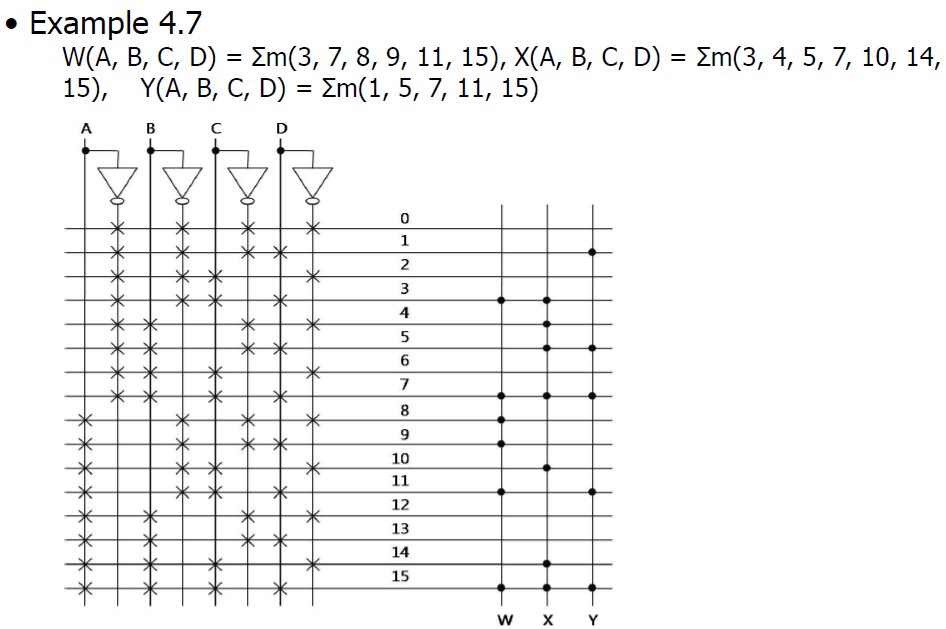

3) 예제

1> 기본 예제

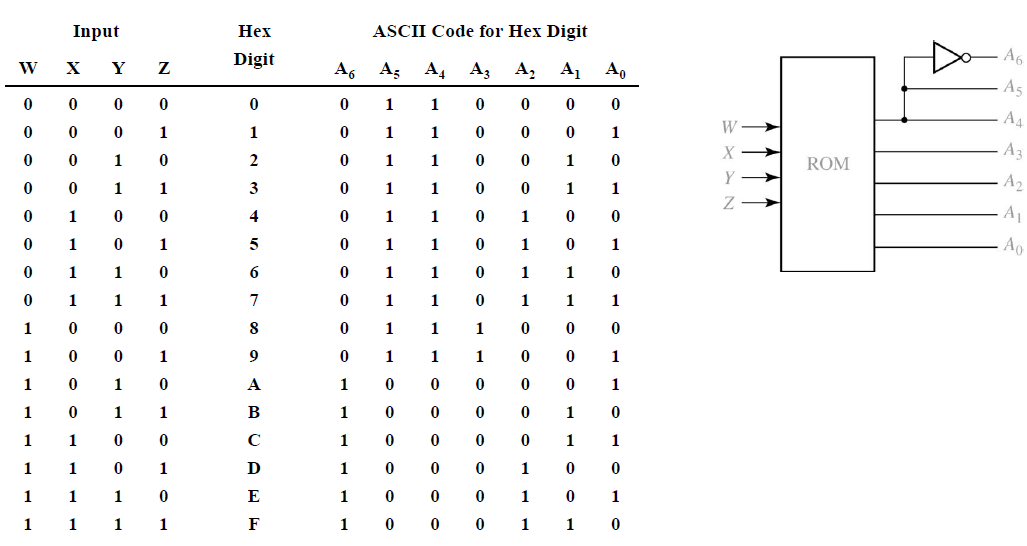

2> Hexadecimal to ASCII Code Converter

9. Programmable Logic Arrays (PLA)

0) ROM의 단점

Full decoder를 쓰기 때문에, 2^m의 input으로 확장된다. 이들을 조합하면 SOP가 되는데

SOP에 대해 1은 적게 가지고 0은 많이 가져서 공간에 대한 낭비가 심하다.

=> 그래서 필요한 만큼만 구현하는 PLA를 사용해본다.

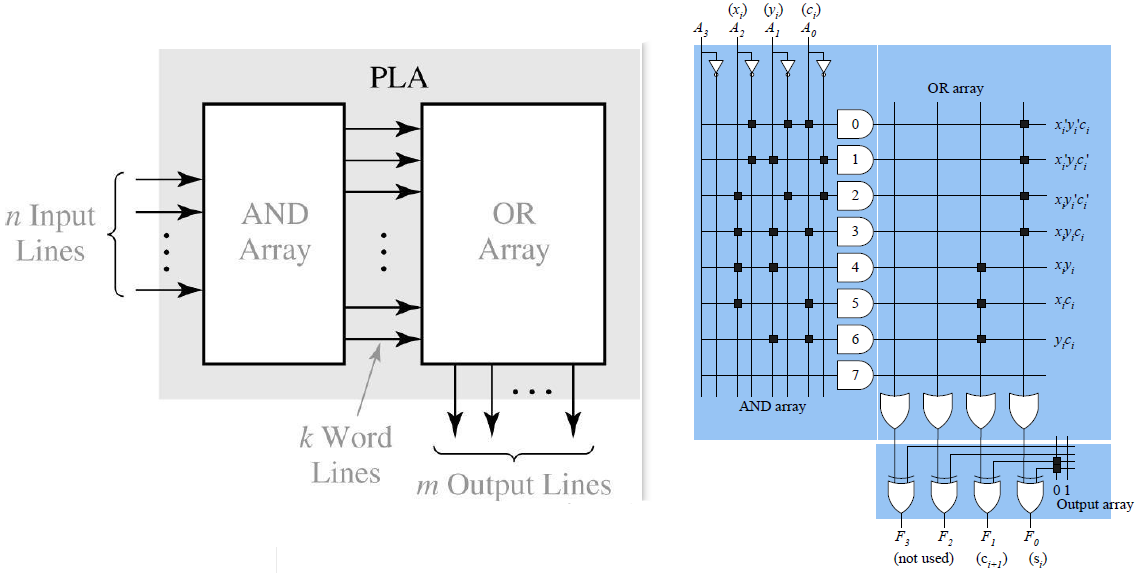

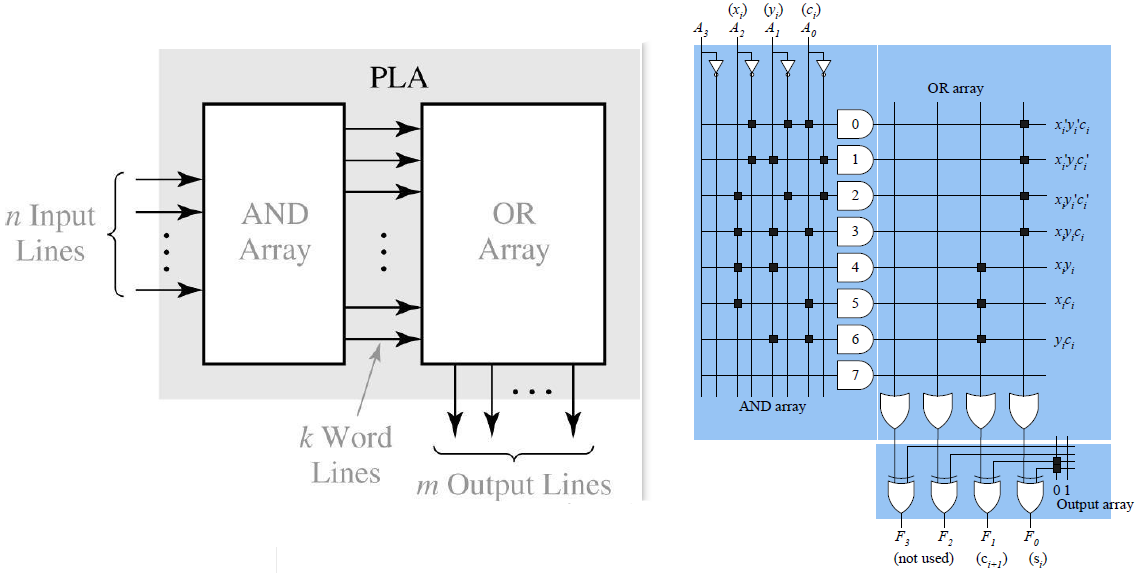

1) PLA의 구조

1> AND array : programmable decoder를 사용한다. (0인 항이 안 생긴다.)

- programmable decoder : AND array를 이용해서 (decoder 대신에) 필요한 부분만 사용하는 decoder

2> OR array : AND array의 결과를 필요한 부분끼리 더해준다.

- programmable

3> output array : programmable output array (output value를 complement 하고 싶을 때 사용한다.)

- programmable

2) PLA의 특징

1> 최적화가 이미 되었기 때문에 ROM보다 변형이 어렵다.

2> 어떤 logic을 구현하더라도 효율적이다.

3> control logic을 구현하는데 주로 사용 (ROM은 부팅과 같은 곳에 주로 사용)

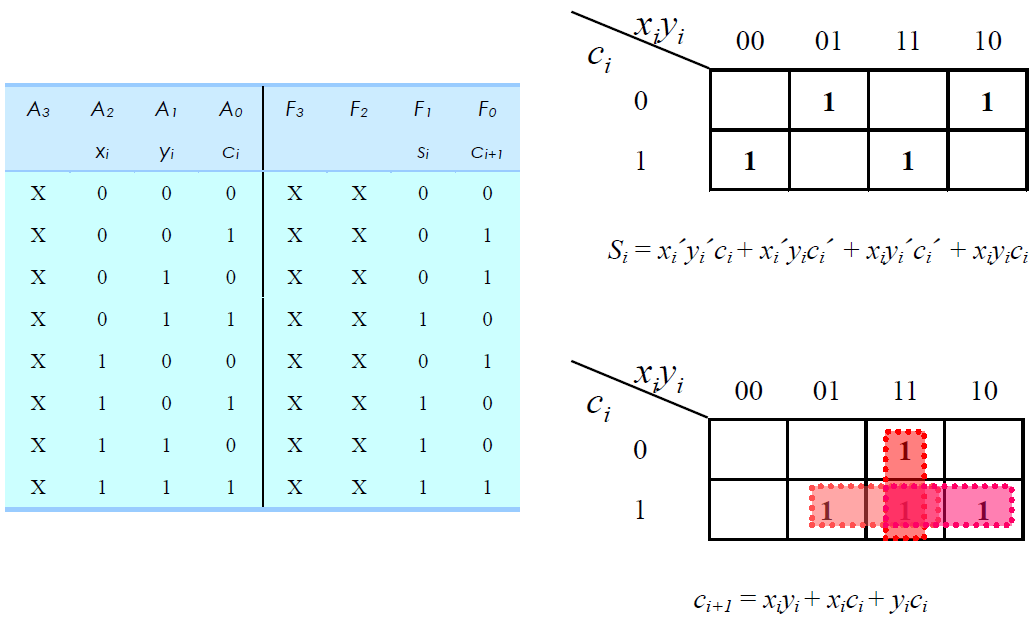

3) 예시

1> Truth Table & K-map

2> 회로 구현

- programmable decoder : AND array를 이용해서 (decoder 대신에) 필요한 부분만 사용하는 decoder

cf>

ROM은 canonical form으로 모든 1에 대해 계산

PLA은 K-map을 기반으로 약간의 간소화를 진행된 것을 decoder의 일부로 사용한다.

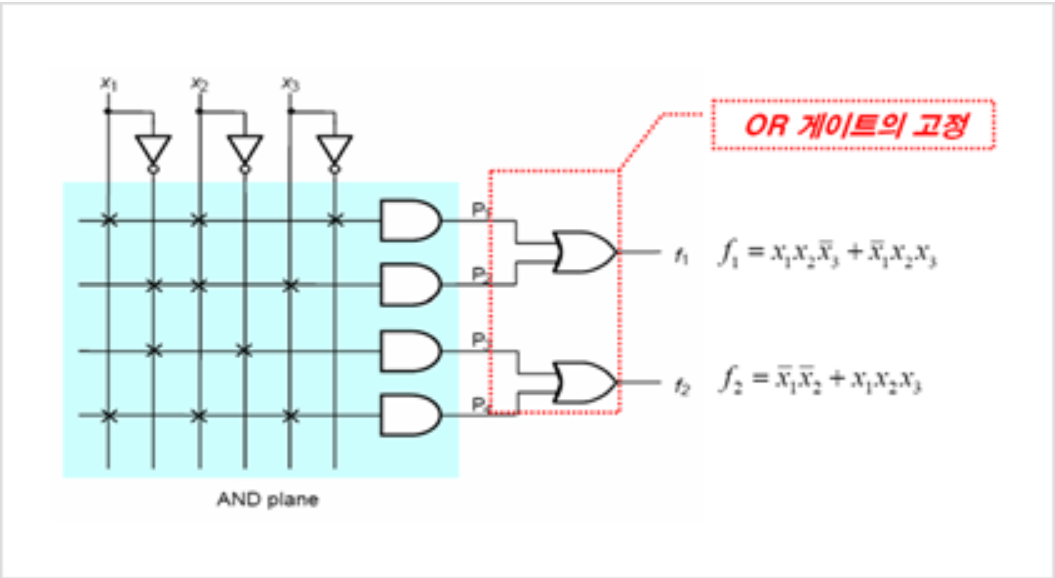

10. Programmable Array Logic

PLA에서 OR array가 빠진 구조이며 그로 인해 필요한 term들을 AND array에서 일일이 만든다.

1) PAL 구조

1> AND array : programmable decoder를 사용한다. (0인 항이 안 생긴다.)

- programmable decoder : AND array를 이용해서 (decoder 대신에) 필요한 부분만 사용하는 decoder

2> OR array : programmable 하지 않고 고정되어 있다. (프로그래밍이 더 수월하다.)

'디지털 회로 개론' 카테고리의 다른 글

| 5-2강 - Analysis of Sequential Systems 2 (Flip Flops) (0) | 2020.11.13 |

|---|---|

| 5-1강 - Analysis of Sequential Systems 1 (Latch) (0) | 2020.11.13 |

| 4-3강 - Combinational System Design 3 (Multiplexers, Bus) (0) | 2020.10.22 |

| 4-2강 - Combinational System Design 2 (Adder/Subtractor, Decoder) (0) | 2020.10.22 |

| 4-1강 - Combinational System Design 1 (Full Adder, Ripple Carry Adder, Carry Look-Ahead Adder) (0) | 2020.10.10 |