4. Adder/Subtractor

select signal이라는 것을 이용해서 덧셈과 뺄셈을 모두 수행할 수 있게 한다.

1) 구성

1> input : A = a_n-1...a_0, B = b_n-1...b_0

2> select signal : S

3> output : F = f_n-1...f_0

2) select signal에 따른 연산

1> S=0

A와 B와의 덧셈을 수행

2> S=1

A와 (1+B')와의 덧셈을 수행

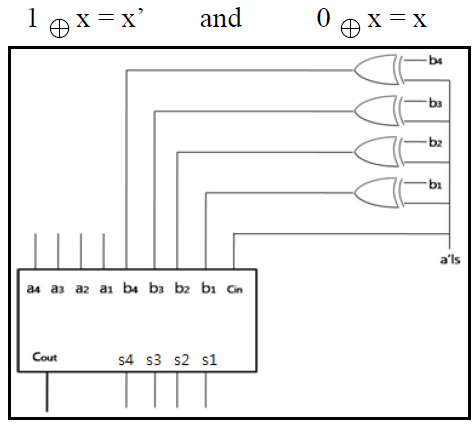

3) 회로도

1> select signal = 0

B가 원래 값 그대로 Adders/Subtractor에 들어갑니다.

select signal은 0이 Adders/Subtractor에 들어갑니다.

수행 연산 : A + B

2> select signal = 0

B가 1과의 XOR 연산으로 B의 complement가 Adders/Subtractor에 들어갑니다.

select signal은 1이 Adders/Subtractor에 들어갑니다.

수행 연산 : A + B' + 1

5. Decoder

1) Decoder

1> 정의 : n-bit (encoded) input을 최대 2^n개의 output으로 변환하는 조합회로

2> 설명

적은 입력 단자로 encoding 된 것을 더 많은 종류의 output으로 변환하는 작업입니다. 즉, computer에게는 최소한의 회로로 encoding 되었던 것을 decoder를 통해 사람이 읽을 수 있도록 해독하는 역할을 합니다.

3> high decoder

decoder의 결과 어떤 부분(0~3)에 해당하는 지를 1로 나타내는 경우이다.

이를 위해 output을 유도하는 부분에 AND gate를 사용합니다.

4> low decoder

decoder의 결과 어떤 부분에 해당하는 지를 0으로 나타내는 경우입니다.

이를 위해 output을 유도하는 부분에 NAND gate를 사용합니다.

NAND gate를 사용하기 때문에 6개의 transistor가 필요한 AND gate보다 비교적 간단하게 구현할 수 있습니다.

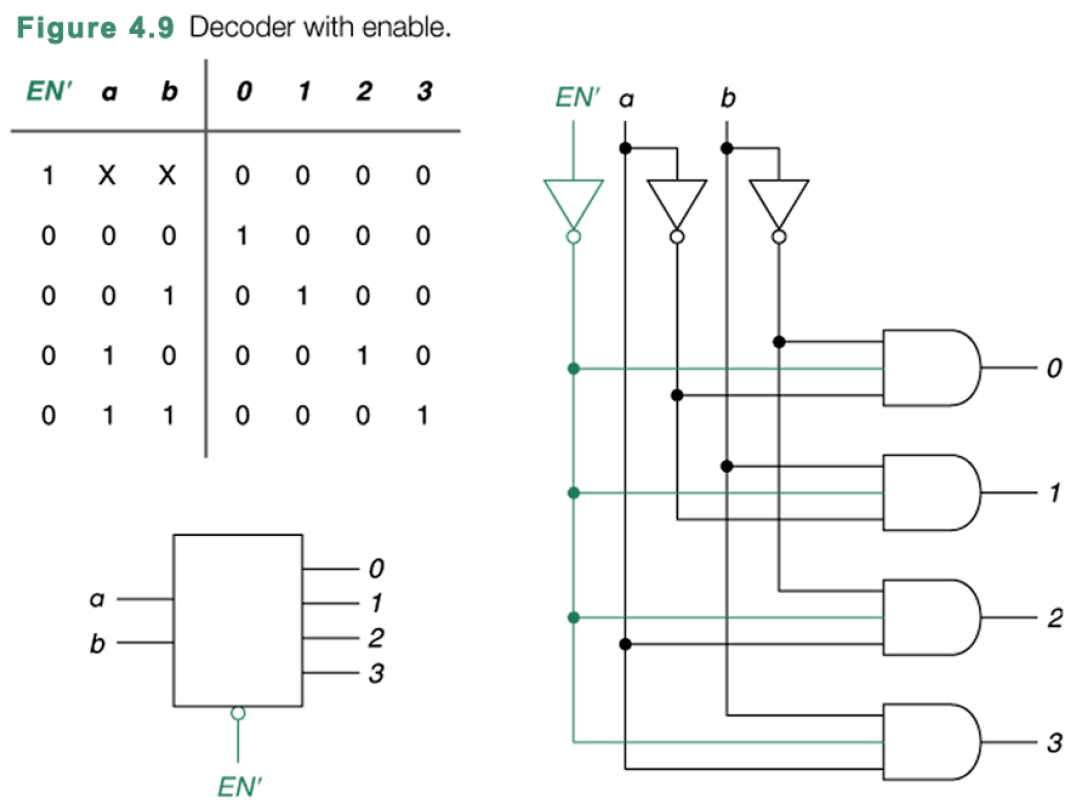

5> enable (항상 존재하는 것은 아니다.)

decoder의 스위치 역할을 한다.

enable이 0이면 decoder가 작동하고, enable이 1이면 decoder가 작동하지 않아 output의 모든 값이 0이 나오게 합니다.

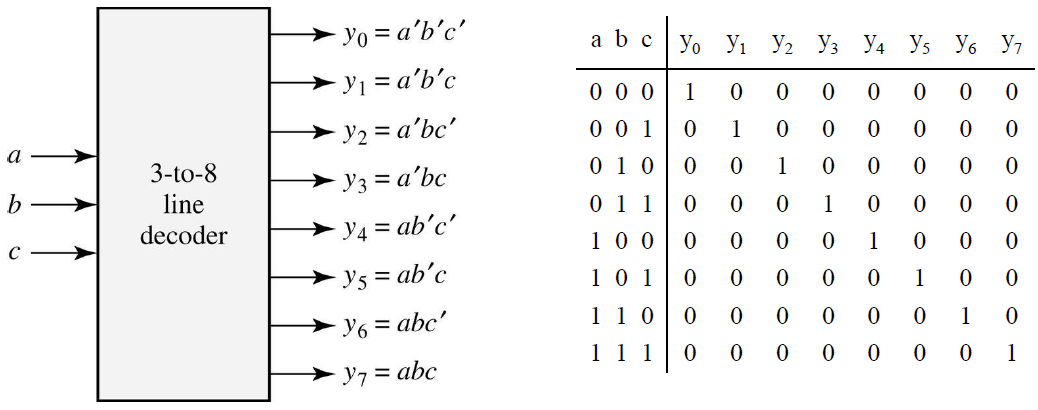

2) Binary Decoder

1> high decoder

- [1] NOT : input이 있고 없고를 표현하기 위해 앞 부분에 NOT을 쓰기도 하고 안 쓰기도 합니다.

- [2] AND : NOT을 통해 input이 있고 없고를 전달받아서 AND gate로 그 조합이 있는지를 check합니다.

2> low decoder

- [1] NOT : input이 있고 없고를 표현하기 위해 앞 부분에 NOT을 쓰기도 하고 안 쓰기도 합니다.

- [2] NAND : NOT을 통해 input이 있고 없고를 전달받아서 NAND gate로 그 조합이 있는지를 check합니다. 그리고 그 조합이 있다면 0으로 표시합니다.

3> high decoder with enable

3) 그 외의 예시

1> 3x8 decoder

2> 4x16 decoder using 2x4 decoders

1st level 1개, 2nd level 4개 => 총 5개의 2x4 decoders를 사용

- 1st level : 2X4 decoder에 a, b를 넣고 -> 결과에 따라 enable이 다음 level의 decoder를 활성화한다.

- 2nd level : 활성화된 decoder가 c, d에 따른 값을 얻는다.

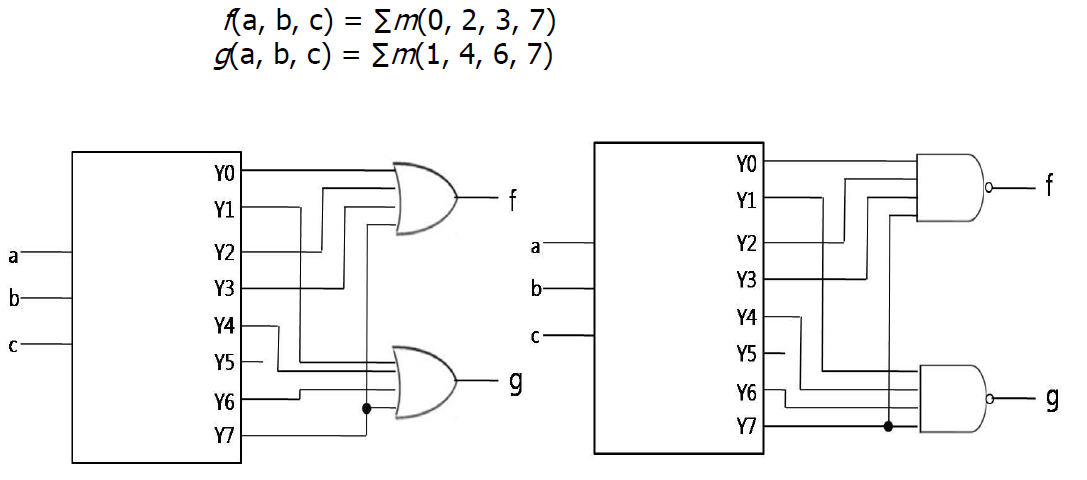

4) Logic function by decoders

decoder의 output이 input에 대한 minterm이기 때문에

logic function도 decoder로 표현 가능하다.

'디지털 회로 개론' 카테고리의 다른 글

| 4-4강 - Combinational System Design 4 (ROM, PLA, PAL) (0) | 2020.10.23 |

|---|---|

| 4-3강 - Combinational System Design 3 (Multiplexers, Bus) (0) | 2020.10.22 |

| 4-1강 - Combinational System Design 1 (Full Adder, Ripple Carry Adder, Carry Look-Ahead Adder) (0) | 2020.10.10 |

| 3-1강 - 카르노 맵 (The Karnaugh Map) (0) | 2020.10.08 |

| 2-1강 - Combinational system 1 (디지털 논리 회로, 논리 연산, 트랜지스터) (0) | 2020.09.24 |