1. Verilog의 기본적인 구조 – module

1) module

module은 Verilog에서 기본 설계 단위이며

이를 통해 다른 모듈을 포함하는 계층적 구성을 할 수 있습니다.

2) Verilog의 기본 구성

머리부, 선언부, 몸체부 등 크게 3가지로 구성됩니다.

1> 머리부

module {모듈 이름} ({port 목록});- 이후에 module 맨 마지막에 endmodule로 module의 끝을 알려야 한다.

2> 선언부

- module에서 필요한 것들을 선언한다.

- C언어에서 변수 선언하는 것과 유사한 부분

- port (port들의 방향, 비트 폭)

- reg

- wire

- parameter

3> 몸체부

회로의 기능, 동작, 구조 등을 표현하는 구문들로 구성

2. Verilog의 기초 문법

1) Verilog Data Type

1> register : 추상적 저장 장치

(즉 value를 저장하는 장치)

reg : 절차형 할당문(always, initial)에 의해 값을 받는 객체

integer : 정수형 변수

time, realtime : 시간형 변수 (시간에 따라 다른 값을 넣고 싶을 때처럼 시간 체크가 필요한 상황에서 simulation 시간을 처리)

real : 실수형 변수

2> Net : 디바이스의 물리적인 연결

(간단히 생각해서 각 Gate 간 연결해주는 부분을 의미한다.)

wire : 변수들이 모듈 내에서 어떻게 연결되어 있는 지를 나타내주는 변수

tri : 선을 연결할 때 사용한다. (tri-state net에 사용한다.)

2) 상수 (constant) 선언

=> bit 수 제한이 있는 reg의 값 선언할 때

{bit 수}‘{입력 형식}{입력 값}1> bit(size) 정한 경우

- 4‘b1111; => binary 1111 (4bit)

- 4’hf; => hexadecimal 1 (4bit)

2> bit(size) 정하지 않은 경우

- 214; => integer 214

- h32; => hexadecimal 32

- o324; => octal 324

3> signed number

- -8’d6; => decimal –6 (8bit)

3) 연산자

1> 연산자

|

|

연산자 |

의미 |

|

산술 연산자 |

+, -, %, *, / |

산술 연산 |

|

관계 연산자 |

==, !=, >, >= |

관계 연산 |

|

논리 연산자 |

&& |

논리적 AND |

|

|| |

논리적 OR |

|

|

! |

논리적 NOT |

|

|

& |

비트 AND |

|

|

| |

비트 OR |

|

|

~ |

비트 NOT |

|

|

^ |

비트 XOR |

|

|

^~, ~^ |

비트 XNOR |

|

|

시프트 연산자 |

>> |

오른쪽 shift |

|

<< |

왼쪽 shift |

|

|

기타 |

{} |

결합 연산자 |

|

{{}} |

반복 연산자 |

|

|

exp1?exp2:exp3 |

3항 조건 연산자 |

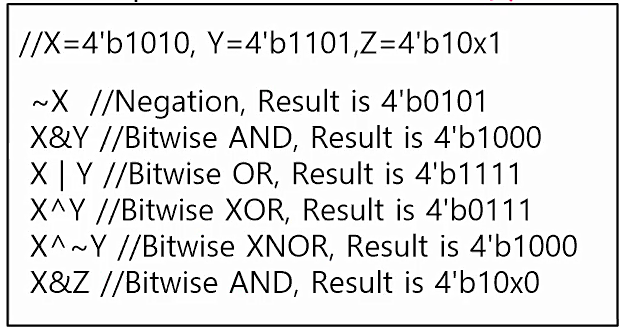

2> 예시 1

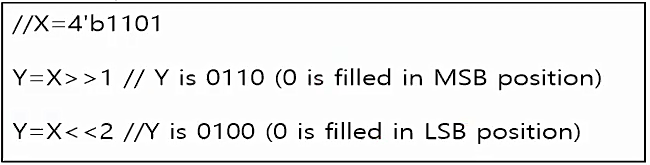

3> 예시 2

verilog에서는 밀려난 bit는 사라진다.

그리고 새로 생긴 자리는 0으로 채워진다.

'디지털 회로 실습' 카테고리의 다른 글

| 2-4강 - vivado 실행 (0) | 2020.09.09 |

|---|---|

| 2-3강 - verilog 기초 3 (기초 구문, Net 형 자료형) (0) | 2020.09.08 |

| 2-2강 - Verilog 기초 2 (기초 문법, 절차형 할당문) (1) | 2020.09.08 |

| 1강 - FPGA (Verilog, VHDL) (0) | 2020.09.03 |