1. FPGA란

1) 정의

Field Programmable Gate Array : 논리 소자 간 내부 회로에 프로그래밍이 가능한 반도체이다.

(field 형태의 바둑판처럼 규칙적인 array 형태)

(사용자가 프로그래밍이 가능한 gate array

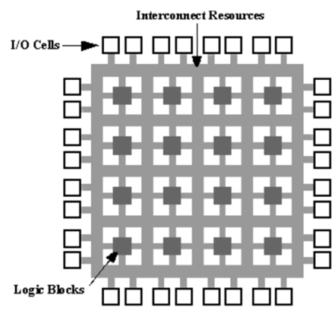

2) 구성

1> (configurable) logic block

flip-flop : 1 bit의 정보를 보관할 수 있는 회로이며 전기 신호가 지속적으로 공급되어야 정보를 유지할 수 있다.

multiplexer : 여러 입력 신호 중 하나를 선택해서 하나의 라인에 전달하는 장치

Look-up Table : table을 검색하는 방식 (여러 gate를 잘 조합하면 내가 원하는 program을 만들 수 있다.)

2> I/O cell

입력 및 출력 회로를 설계 용도에 맞게 구성하기 위한 회로들이 있다.

3> interconnection resource (배선 영역)

아래 2가지로 구성 (이 때, 배선의 길이는 FPGA의 구조에서 중요한 역할을 한다.)

배선 와이어 : logic block 사이의 신호 or logic block과 I/O cell을 연결

전기적 연결 스위치 : 배선 와이어와 와이어 사이를 연결

3) 특징

1> programmable

- 일반적인 반도체는 회로 변경과 프로그래밍이 불가능합니다. 하지만 FPGA는 programmable해서 사용자가 내부 회로를 마음대로 프로그래밍으로 바꿀 수 있습니다.

- FPGA를 구성하는 논리 소자(PLD : programmable logic device)는 AND, OR, XOR, NOT, 더 복잡한 디코더나 계산 기능의 조합과 같은 기본적인 기능들 프로그래밍에 사용할 수 있다.

2> SRAM 프로그래밍

SRAM 방식은 전원이 OFF되면 연결점을 제어하기 위한 configuration 정보를 유실하는 휘발성 기억소자입니다. 그래서 ON/OFF 정보를 저장하고 시스템을 초기화 할 때 FPGA의 SRAM을 다운받는데 ON/OFF 정보를 사용한다.

2. 활용법 및 사용법

1) 초기 설계 입력

1> 그래픽적인 입력

schematic capture tool을 통해 논리 회로를 입력한다. 내부의 라이브러리들은 FPGA의 칩 구조를 기반으로 해서 미리 설계된 기능을 가진 회로들로 구성되어 있다. 그로 인해 안정적이고 효율적이다.

2> 문자적인 입력

그래픽적인 입력 외에도 문자적인 방법으로 부울식, HDL, VHDL, Verilog HDL에 의한 입력을 사용한다. 그래픽적인 입력으로만 프로그래밍을 하면 전체적인 논리를 파악하기 힘들 수 있는데 그래서 문자적인 방식도 자주 사용한다.

2) RTL simulation (register-transfer level simulation)

이전 과정에서 사용자가 구현한 것을 simulation으로 검증하는 단계이다.

1> register란 보통 filp-flop으로 구성되며 clock 신호가 들어가서 회로를 동기화하는 역할을 한다. 그리고 메모리처럼 데이터를 읽고 쓸 수 있다.

2> HDL 코드에서는 이러한 register들을 마치 변수처럼 선언해서 사용한다. 그래서 HDL로는 실제 디지털 회로가 어떻게 구현될지는 알 수 없지만 register level에서는 대략적으로 알 수 있다.

3> 뒤에 이어질 synthesis 과정을 거친 뒤에 FPGA 보드에 넣어서 테스트하기도 합니다. 하지만 synthesis 시간이 오래 걸리고 디버깅이 어렵기 때문에 합성 전에 거쳐갑니다.

4> 그런데 간혹 RTL simulation 과정을 정상적으로 넘어가도 합성이 안 되는 경우도 있습니다. 그래서 synthesis 이후에도 확인할 필요가 있습니다.

3) synthesis

유저가 구현한 high-level 디자인을 FPGA 보드가 이해할 수 있는 low level로 바꿔주는 단계이다. HDL 코드를 합성해서 netlist 형태의 data로 만든다. HDL(RTL)이었던 코드를 실제 디지털 회로로 구현하는 것이다.

cf> logic optimization

FPGA의 한정된 gate 자원을 최대로 사용하기 위한 최적화 단계

(Synplify, LeonardoSpectrum 및 FPGA Compiler와 같은 특별한 CAD tool을 이용한다.)

cf> technology mapping

여러 개의 FPGA에 설계된 회로를 나누어 구현하고 각 부분들이 FPGA의 logic block들을 사용한 회로에 맞게 변환되는 과정

4) Place & Route

실제적인 회로의 구현 형태가 FPGA의 칩 상에 이루어진 단계

1> Place (배치)

mapping된 block들을 FPGA의 특정 logic block 위치에 지정하는 단계

2> Route (배선)

배치된 각 block들을 회로의 연결 정보에 따라 연결 연결선 및 전기적 스위치를 사용하여 상호 연결하는 단계

5) 설계 검증 및 성능 추정

1> P&R이 끝나고 실제 회로의 형태를 가지고 있는 상황에서 timing simulation을 진행

P&R 직후에 cell들을 연결하면 wire의 길이가 달라질 수 있습니다. 이 때 delay 문제가 생길 수 있습니다. 이와 같은 timing error가 없이 회로가 잘 돌아가는지 검증하는 과정입니다.

2> 또한, 어떤 조건에서 어떤 performance를 발휘하는지도 측정하고 추후 어떤 성능을 가질지 추정합니다.

3. 장점

1) 속도

하드웨어의 병렬성을 기반으로 해서 (순차적이지 않다.) 클럭 주기당 더 많은 작업 수행을 한다. 그래서 속도가 빠르다. 따라서 신호 처리가 중요한 분야에서 주로 사용한다.

2) 안정성

프로세서 기반의 시스템은 어떠한 프로세서 코어든지 하나의 task를 한 번에 실행하며 시간 결정적 task의 위험 상태에서 서로를 선점합니다. 그로 인해 결정성 있는 하드웨어로 안정성 문제를 최소로 줄여줍니다.

<ASIC와 비교한 장점들>

3) 시장 출시 기간

ASIC 디자인은 긴 제조 과정을 거쳐야 하지만 FGPA는 그러지 않고도 아이디어나 개념을 하드웨어에서 검증할 수 있습니다. 또한 상용 하드웨어는 FPGA 칩에 연결된 다른 유형의 I/O와도 사용할 수 있습니다.

이러한 검증 기간의 단축과 범용성 덕분에 시장에 출시되기까지의 기간이 ASIC보다 짧습니다.

4) 비용

여러 유저들은 맞춤 하드웨어 기능을 필요로 합니다. FPGA는 요구에 따라 점진적으로 변경해나가는 비용이 ASIC를 새로 구축하는 것보다 적게 들어갑니다.

5) 장기 유지 관리

프로그래밍이 가능하며 현장에서 바로 업그레이드가 가능한 FPGA의 특성상 재설계를 할 필요 없이 바로 필요한 만큼 업그레이드를 하면 되기 때문에 장기적으로 유지할 수 있다는 측면에서 장점이 있습니다.

4. 단점

1) 대량으로 생산했을 때 비용이 많이 들어갑니다.

ASIC는 한 번 구축하면 양산했을 때의 비용은 적습니다. 하지만 FPGA의 양산 단가는 비쌉니다.

2) 칩의 면적이 크다.

그로 인해 작은 사이즈의 제품은 FPGA로 설계하기 어렵다.

5. 활용 분야

위의 장단점으로 보아 FPGA는 빠르고 안정적인 하드웨어 프로그래밍을 요구하는 분야에 사용됩니다.

1) 로봇

2) AI

단순 matrix 연산을 많이 처리해야 하는 특성상 병렬적인 연산을 하는 FPGA가 AI에 적합합니다.

3) 디지털 신호 프로세서 라디오

4) ASIC 초기 버전

빠른 검증이 가능한 FPGA의 특성상 양산할 ASIC를 검증하기 위해 초기 버전을 만드는데 사용할 수 있다.

6. HDL

1) HDL

1> 이름

Hardware description language

말 그대로 하드웨어(전자 회로)의 특징(기능 및 동작)을 기술하는데 사용하는 컴퓨터 언어입니다. 즉, 디지털 시스템의 기능 및 하드웨어 특징을 컴퓨터의 고급 언어에 접합하여 원하는 회로를 기술할 수 있도록 하는 언어입니다.

프로그래밍 언어처럼 문법에 맞게 코드를 작성하면 Design Tool에서 이를 적절한 Gate의 집합으로 치환시켜줍니다. 치환된 Gate의 묶음은 이후 회로의 수많은 Translator로 적용됩니다.

2> 특징

concurrency (동시성)

parallel (병렬성)

abstraction (추상화)

2) VHDL

저희가 앞으로 배울 언어는 Verilog이지만 그 외에는 대표적으로 VHDL이 있습니다.

1> 이름

VHDL : VHSIC Hardware Description Language

VHSIC : Very-High-Speed Integrated Circuits (초고속 집적 회로)

2> 특징

Verilog에 비해 더 high-level modeling이 가능합니다.

pascal과 유사한 문법을 가집니다.

3) Verilog의 역사와 발전 과정

(1983년)

verilog는 Prabhu Goel이 세운 Gateway Design Automation 회사에서 1983년에 해당 언어와 simulator를 공개했습니다.

(1985년)

새 version의 verilog인 verilog-XL과 simulator를 공개했습니다.

(1989년~1995년)

Cadence 회사가 Gateway를 인수하여 Verilog HDL을 공개합니다. 그로 인해 open verilog interation이 만들어져서 사용자가 늘어나기 시작합니다. 특히 IEEE표준이 만들어져서 Verilog-95(IEEE 1364-1995)로 불리게 됩니다.

(2001년)

Verilog-2001로의 업그레이드가 있었습니다. 업데이트 내역은 아래와 같습니다.

- 2의 보수와 변수의 지원이 추가되었습니다.

- 파일 입출력이 새로운 시스템 작업으로 업그레이드

C style의 함수라든지 등등의 새로운 syntax의 추가

(2005년)

Verilog-2005로의 업그레이드가 있었고

디지털 시스템의 설계에서 검증의 필요성이 점차 커짐에 따라 이를 지원하기 위한 SystemVerilog 업그레이드가 있었습니다. 이 또한, IEEE 표준으로 만들어졌습니다.

'디지털 회로 실습' 카테고리의 다른 글

| 2-4강 - vivado 실행 (0) | 2020.09.09 |

|---|---|

| 2-3강 - verilog 기초 3 (기초 구문, Net 형 자료형) (0) | 2020.09.08 |

| 2-2강 - Verilog 기초 2 (기초 문법, 절차형 할당문) (1) | 2020.09.08 |

| 2-1강 - Verilog 기초 1 (module, 기초 문법) (0) | 2020.09.07 |